# Investigation on Dynamic Voltage Restorers With Two DC Links and Series Converters for Three-Phase Four-Wire Systems

Gregory A. A. Carlos\*†, Cursino B. Jacobina† and Euzeli C. dos Santos Jr.‡

\* DCIP - Federal Institute of Alagoas (IFAL) - Alagoas - Brazil

† DEE - Federal University of Campina Grande (UFCG) - Paraíba - Brazil

‡DECE - Purdue School of Engineering and Technology (IUPUI) - Indiana - USA

Abstract—This paper proposes three dynamic voltage restorer (DVR) topologies. Such configurations are able to compensate voltage sags/swells in three-phase four-wire (3P4W) systems under balanced and unbalanced conditions. The proposed systems use two independent dc links. Proposed configurations present advantages in terms of switch blocking voltages and consequently lower dc-link voltage rating. The complete control system, including the PWM technique, is developed and comparisons between the proposed configurations and a conventional one are performed. Simulation and experimental results are provided to validate the theoretical approach.

Index Terms—Dynamic voltage restorer (DVR), open-end winding (OEW) transformer, three-phase four-wire system, multilevel inverter.

#### **NOMENCLATURE**

| i                                      | Subscript associated for each system phase $j = 1, 2, 3$ .             |  |  |  |  |

|----------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| $_{k}^{j}$                             | Subscript associated for each converter wire $k = 1, 2, 3, 4$ .        |  |  |  |  |

| $q_{ak}, \overline{q}_{ak}$            | Homonymous binary variable and its complementary value                 |  |  |  |  |

| ian, ian                               | for converter A.                                                       |  |  |  |  |

| $q_{bk}, \overline{q}_{bk}$            | Homonymous binary variable and its complementary value                 |  |  |  |  |

| 10107 101                              | for converter B.                                                       |  |  |  |  |

| $v_{ak0a}$                             | Pole voltages for converter A.                                         |  |  |  |  |

| $v_{bk0b}$                             | Pole voltages for converter B.                                         |  |  |  |  |

| $v_{rk}$                               | Resultant converter output voltages $(v_{rk} = v_{ak0a} - v_{bk0b})$ . |  |  |  |  |

| $v_{pj}$                               | Phase voltages of injection transformers.                              |  |  |  |  |

| $v^*$ ,                                | References for auxiliary variables in the PWM strategy.                |  |  |  |  |

| $u^*$ ,                                | Parameters used to compute $v_{xk}^*$ .                                |  |  |  |  |

| $v_{xk}^{r_J} \ \mu_{xk}^* \ v_{r4}^*$ | Reference for fourth wire auxiliary variable in the PWM                |  |  |  |  |

| $r_4$                                  | strategy.                                                              |  |  |  |  |

| $\mu_{r4}^*$                           | Parameter used to compute $v_{r4}^*$ .                                 |  |  |  |  |

| $v_{ca}, v_{ca}^*$                     | Dc-link voltage for converter A and its reference.                     |  |  |  |  |

| $v_{cb}, v_{cb}^*$                     | Dc-link voltage for converter B and its reference.                     |  |  |  |  |

| $v_{cab}^*$                            | Average dc-link reference voltage.                                     |  |  |  |  |

| WTHD                                   | Weighted total harmonic distortion.                                    |  |  |  |  |

| IGBT                                   | Insulate gate bipolar transistor.                                      |  |  |  |  |

| DSP                                    | Digital signal processor.                                              |  |  |  |  |

| $f_s$                                  | Switching frequency.                                                   |  |  |  |  |

| $f_{o}$                                | Fundamental system frequency.                                          |  |  |  |  |

| 4L                                     | Terminology used for conventional four-leg converter.                  |  |  |  |  |

| 2C                                     | Terminology used for conventional split-capacitor converter.           |  |  |  |  |

| 3HB                                    | Terminology used for conventional three-H-bridge converter.            |  |  |  |  |

| 2C2C                                   | Terminology used for proposed combined 2C-2C converter.                |  |  |  |  |

| 4L2C                                   | Terminology used for proposed combined 4L-2C converter.                |  |  |  |  |

| 4L4L                                   | Terminology used for proposed combined 4L-4L converter.                |  |  |  |  |

| NPC                                    | Terminology used for multilevel neutral-point-clamped                  |  |  |  |  |

|                                        | converter.                                                             |  |  |  |  |

| 4LNPC                                  | Terminology used for four-leg NPC converter.                           |  |  |  |  |

| CHB                                    | Terminology used for cascaded H-Bridge converter.                      |  |  |  |  |

| D T T                                  | 51 1 1 1 1                                                             |  |  |  |  |

PLL

Phase-locked loop.

$\begin{array}{ll} ESR & \text{Equivalent series resistance.} \\ P_{loss}^{HO} & \text{Dc-link high frequency power losses.} \\ C_f, C & \text{Filtering capacitor and dc-link capacitor.} \end{array}$

# I. INTRODUCTION

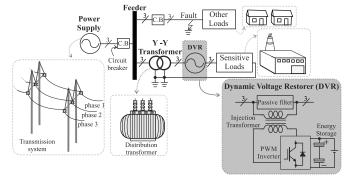

Every year, the industry and commerce sector lose billions of dollars due to problems associated to power quality [1], [2]. Because of this fact, voltage sags have been reported as a major power-quality problem [3], [4]. In this way, dynamic voltage restorer (DVR) has been pointed out as the most attractive solution for this issue [5]–[10]. Such a customized power device is extremely suitable for protecting sensitive loads from voltage sags [10], [11]. The DVR is constituted by injection transformer, energy storage devices, passive filters (e.g., filtering capacitors) and PWM inverters, as observed in Fig. 1. This device is most applicable in distribution systems [6], [10] where voltage sags occur most commonly.

Fig. 1. Typical DVR location in a 3P4W power distribution system.

There are two types of power distribution systems when their transformers are considered: i) three-phase three-wire (3P3W) and ii) three-phase four-wire (3P4W).  $\Delta Y$  transformer winding connection seems to be a good arrangement option since it prevents zero sequence components from propagating to the secondary side of the transformer when an unbalanced fault occurs on the primary side network [12]. However, countries such as China and Korea [10], [12] commonly use a YY winding with neutrals grounded, see Fig. 1. In this case,

978-1-4799-5776-7/14/\$31.00 © 2014 IEEE

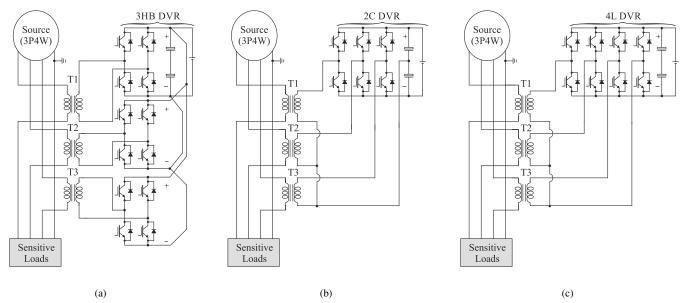

Fig. 2. Existing DVR configurations in 3P4W distribution system using injection transformers. (a) Conventional three H-Bridge (3HB) [10]. (b) Split-capacitor (2C) [12]. (c) Four-leg (4L) [13].

propagation of zero sequence components to the loads are allowed when an unbalanced fault takes place [14]. The zero sequence components propagation problem has been solved with some existing DVR topologies, see Fig. 2.

DVR technology has became a mature power quality product. Many advances have been documented in technical literature considering different aspects [8], [15]-[27]. For instance, the integration of photovoltaic and DVR systems has been proposed and validated experimentally via nine-switch converter topology in [16]. The authors in [18] focused on proposing a new phase-locked loop (named soft-PLL) and voltage sag detection algorithm based on least error square (LES) and symmetrical components method to improve the DVR performance. It was shown that the traditional algorithm achieved the steady state operation after 11 ms, while 3 ms was obtained with the proposed algorithm in [18]. The converter topology considered in that work was a cascaded H-Bridge inverter. Major studies have been validated with an experimental test rated at 10 kV [7], [17], [18], [25]. The saturation from injection transformers is another issue considered in the DVR researches. Hence, a method to avoid the saturation of transformers was proposed in [19].

It can be seen that each converter topology considered in these studies have benefits and drawbacks. So the topology selection becomes a particular design criteria to be chosen. Generally, the design criteria lies on: i) low harmonic distortion, ii) low electromagnetic interference and iii) high-voltage operation capability that is accomplished by using series connected switches. Hence, DVRs associated with a multilevel based inverter can be used to achieve most of those desirable features. In this way, a four-leg neutral point clamped (4LNPC) [28] inverter has been investigated with an optimized PWM technique. Similar results were obtained by means of a

space vector PWM algorithm applied in a cascaded H-bridge (CHB) [29]. Multilevel equivalent results can be achieved by considering the concept of open-end winding (OEW) at the injection transformers of DVRs. The OEW concept is widely used in 3P3W motor drive systems [30] and recently on DVR for 3P3W systems [31].

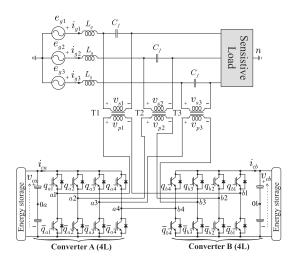

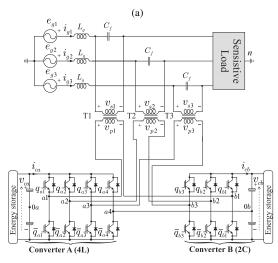

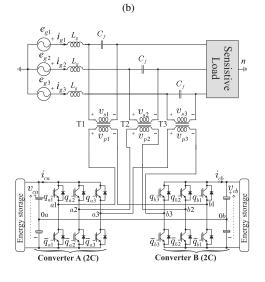

This work investigates three options for a DVR topology on 3P4W systems application (see Fig. 3) based on the concept of OEW. Configuration 4L4L, is based on two four-leg (4L) inverters connected to injection transformers (see Fig. 3(a)). Configuration 4L2C (see Fig. 3(b)) consists of a four-leg (4L) inverter connected at one side (i.e., converter A) and split capacitor (2C) at the other side (i.e., converter B). The third one, configuration 2C2C (see Fig. 3(c)) is composed of two split capacitor (2C) configurations connected to an injection transformer in an OEW arrangement. They use more power switches than conventional ones, but enables the converter to operate with: i) lower dc-link voltage rating which reduces the switch blocking voltages and ii) lower harmonic distortion at the injected voltages by the DVR due to operation with asymmetrical dc-link voltage. Such features are the main benefits of the proposed configurations. Control system, including the PWM technique, is presented and comparisons between proposed and conventional configurations are performed. Simulation and experimental results are provided for validation purposes.

# II. Models of the proposed DVR systems

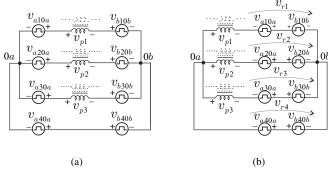

The proposed DVR configurations for 3P4W systems are described in Fig. 3. All of them are based on the concept of OEW. In order to improve the paper readability, the equivalent circuit of configuration 4L4L is presented in Fig. 4(a). The modified model shown in Fig. 4(b) permits to clearly introduce the resultant output converter voltages  $(v_{rk})$  associated for this

(c) Fig. 3. Proposed OEW based DVR configurations. (a) 4L4L. (b) 4L2C and (c) 2C2C.

configuration. The model for the other configurations (i.e., 4L2C and 2C2C) is achieved by particular considerations of voltage  $v_{r4}$  (i.e.,  $v_{r4} = v_{a40a}$  for 4L2C and  $v_{r4} = 0$  for 2C2C).

Fig. 4. Equivalent circuit for configuration 4L4L. (a) Original. (b) Modified.

The pole voltages of each configuration are given by  $v_{ak0a}$ (for converter A) and  $v_{bk0b}$  (for converter B) with k =1, 2, 3, 4. Such pole voltages depend on the conduction states of the power switches. The conduction state of all switches can be represented by the homonymous binary variable (e.g., for converter A  $q_{ak} = 1$  indicates a closed switch while  $q_{ak} = 0$ indicates an open one). Then, the pole voltages  $v_{ak0a}$  and  $v_{bk0b}$ are defined, as follows

$$v_{ak0a} = 0.5v_{ca}(2q_{ak} - 1)$$

(1)

$v_{bk0b} = 0.5v_{cb}(2q_{bk} - 1)$  (2)

$$v_{bk0b} = 0.5v_{cb}(2q_{bk} - 1) (2)$$

# A. Configuration 4L4L

From Figs. 3(c) and 4(a), the voltage model of configuration 4L4L is obtained as

$$v_{pj} = v_{rj} - v_{r4} \tag{3}$$

where variable j = 1, 2, 3 and

$$v_{rj} = v_{aj0a} - v_{bj0b} (4)$$

$$v_{r4} = v_{a40a} - v_{b40b} (5)$$

Note that  $v_{r4}$  is the voltage between the midpoints 0a and 0b, see Fig. 4(b). Along the text k = 1, 2, 3, 4 and j = 1, 2, 3.

# B. Configuration 4L2C

In this configuration, the voltage  $v_{pj}$  remains the same as in (3). However, it should be noted that  $v_{r4} = v_{a40a}$  since  $v_{b40b} = 0$  which is connected to the middle point of the dclink.

# C. Configuration 2C2C

This configuration has a similar model compared to conventional 3HB with regard to operation with different dc-link values. The voltages  $v_{pj}$  remain as that in (3) with  $v_{r4} = 0$ .

# III. PWM STRATEGY

In this section, only configuration 4L4L is described in details because the PWM strategy for the other ones (4L2C) and 2C2C) are obtained by particular considerations involving the reference pole voltages of the fourth leg, as discussed next.

#### A. Configuration 4L4L

It can be seen from Figs. 3(a) and 4(a) that it will be necessary to calculate eight reference pole voltages (i.e.,  $v_{ak0a}^*$  and  $v_{bk0b}^*$  with k=1,2,3,4) from three reference voltages  $(v_{p1}^*, v_{p2}^*$  and  $v_{p3}^*$ ) defined from the controllers. Hence, from the degrees of freedom that system offers, five auxiliary variables are introduced, named  $v_{r4}^*$ ,  $v_{x1}^*$ ,  $v_{x2}^*$ ,  $v_{x3}^*$ ,  $v_{x4}^*$ , to determine  $v_{ak0a}^*$  and  $v_{bk0b}^*$ .

From (3)-(5) we introduce the reference voltages  $v_{rj}^*$  and  $v_{r4}^*$  ( $v_{r4}^*$  is one of the auxiliary variables) as follows

$$v_{rj}^* = v_{aj0a}^* - v_{bj0b}^* = v_{pj}^* + v_{r4}^*$$

(6)

$$v_{r4}^* = v_{a40a}^* - v_{b40b}^* \tag{7}$$

Introducing the last four auxiliary variables  $v_{x1}^*$ ,  $v_{x2}^*$ ,  $v_{x3}^*$ ,  $v_{x4}^*$ , the reference pole voltages are written as follows

$$v_{ak0a}^* = \frac{1}{2}v_{rk}^* + v_{xk}^* \tag{8}$$

$$v_{bk0b}^* = -\frac{1}{2}v_{rk}^* + v_{xk}^* \tag{9}$$

To calculate the reference pole voltages  $v_{ak0a}^*$  and  $v_{bk0b}^*$ , it is necessary to calculate first the auxiliary variables  $v_{r4}^*$ ,  $v_{x1}^*$ ,  $v_{x2}^*$ ,  $v_{x3}^*$ ,  $v_{x4}^*$ . However, the limits of the pole voltages  $(\pm v_{ca}^*/2)$  and  $\pm v_{cb}^*/2$  for the converters A and B, respectively) must be respected. The normalized choice of the auxiliary variable voltages satisfying their limits, can be provided by introducing a parameter  $\mu$  ( $0 \le \mu \le 1$ ) for each one (e.g.,  $v_{r4}^* \to \mu_{r4}^*$ ,  $v_{x1}^* \to \mu_{r1}^*$ ,  $v_{r2}^* \to \mu_{r2}^*$ ,  $v_{r3}^* \to \mu_{r3}^*$  and  $v_{r4}^* \to \mu_{r4}^*$ ).

$\rightarrow \mu_{x1}^*, \ v_{x2}^* \rightarrow \mu_{x2}^*, \ v_{x3}^* \rightarrow \mu_{x3}^*$  and  $v_{x4}^* \rightarrow \mu_{x4}^*$ ). Given  $v_{pj}^*$  from (6) and (7), the voltage  $v_{r4}^*$  is first determined according with the following expressions

$$v_{r4}^* = \mu_{r4}^* v_{r4\,\text{max}}^* + (1 - \mu_{r4}^*) v_{r4\,\text{min}}^* \tag{10}$$

with

$$v_{r4\min}^* = -v_{cab}^* - \min\{v_{p1}^*, v_{p2}^*, v_{p3}^*, 0\}$$

(11)

$$v_{r4\max}^* = v_{cab}^* - \max\{v_{p1}^*, v_{p2}^*, v_{p3}^*, 0\}$$

(12)

where  $v_{cab}^* = (v_{ca}^* + v_{cb}^*)/2$  is the average dc-link capacitor reference voltage.

Once  $v_{r4}^*$  is calculated, the reference voltages  $v_{rj}^*$  are calculated from (6) and consequently all  $v_{rk}^*$  are determined. From (8) and (9) the reference voltages  $v_{xk}^*$  are calculated as

$$v_{xk}^* = \mu_{xk}^* v_{xk\,\text{max}}^* + (1 - \mu_{xk}^*) v_{xk\,\text{min}}^* \tag{13}$$

with

$$v_{xk \min}^* = max\{v_{xak \min}^*, v_{xbk \min}^*\}$$

(14)

$$v_{xk\,\text{max}}^* = min\{v_{xak\,\text{max}}^*, v_{xbk\,\text{max}}^*\}$$

(15)

where

$$v_{xak\,\text{min}}^* = -v_{ca}^*/2 - v_{rk}^*/2 \tag{16}$$

$$v_{xbk\,\text{min}}^* = -v_{cb}^*/2 + v_{rk}^*/2 \tag{17}$$

$$v_{xak\,\text{max}}^* = v_{ca}^*/2 - v_{rk}^*/2 \tag{18}$$

$$v_{xbk\,\text{max}}^* = v_{cb}^*/2 + v_{rk}^*/2 \tag{19}$$

The following algorithm summarizes the PWM strategy applied for configuration 4L4L.

Step 1: Determine  $v_{r4}^*$ .

- a) Given  $v_{pj}^*$ , determine  $v_{r4\,\mathrm{min}}^*$  and  $v_{r4\,\mathrm{max}}^*$  using relations (11) and (12), respectively;

- b) Choose  $\mu_{r4}^*$  and determine  $v_{r4}^*$  using (10);

Step 2: Determine  $v_{rj}^*$  from (6).

Step 3: Determine  $v_{xk}^*$ .

- a) From  $v_{rk}^*$ , determine  $v_{xk\, {\rm min}}^*$  and  $v_{xk\, {\rm max}}^*$  using relations (14) and (15), respectively;

- b) Choose  $\mu_{xk}^*$  and determine  $v_{xk}^*$  using (13);

Step 4: Determine  $v_{ak0a}^*$  and  $v_{bk0b}^*$  using relations (8) and (9), respectively.

The modified model obtained by considering voltages  $v_{rk}^*$  (i.e.,  $v_{rj}^*$  and  $v_{r4}^*$ ) is observed in Fig. 4(b). It indicates that once calculated  $v_{rk}^*$  from steps 1 and 2, the steps 3 and 4 correspond to apply a PWM strategy to solve the pole voltages for four H-bridge inverters.

# B. Configuration 4L2C

In this configuration, there are only four auxiliary variables  $(v_{r4}^*, \ v_{x1}^*, \ v_{x2}^*$  and  $v_{x3}^*$ ). The reference pole voltage  $v_{a40a}^*$  is equal to  $v_{r4}^*$ . In this case,  $v_{r4\,\mathrm{min}}^*$  and  $v_{r4\,\mathrm{max}}^*$  are given by

$$v_{r4\,\text{min}}^* = \max\{v_{r4\,\text{min}}'^*, v_{r4\,\text{min}}''^*\}$$

$$v_{r4\,\text{max}}^* = \min\{v_{r4\,\text{max}}'^*, v_{r4\,\text{max}}''^*\}$$

where

$$\begin{array}{lcl} v_{r4\,\mathrm{min}}^{\prime *} & = & -v_{cab}^{*} - \min\{v_{p1}^{*}, v_{p2}^{*}, v_{p3}^{*}\} \\ v_{r4\,\mathrm{max}}^{\prime *} & = & v_{cab}^{*} - \max\{v_{p1}^{*}, v_{p2}^{*}, v_{p3}^{*}\} \\ v_{r4\,\mathrm{min}}^{\prime \prime *} & = & -v_{ca}^{*}/2 \\ v_{r4\,\mathrm{max}}^{\prime \prime *} & = & v_{ca}^{*}/2 \end{array}$$

After steps 1 and 2, steps 3 and 4 solve the pole voltages for three full H-bridges and one half H-bridge.

# C. Configuration 2C2C

For this configuration, there are six pole voltages. Hence, the PWM strategy have only three auxiliary variable voltages  $(v_{x1}^*, v_{x2}^*, v_{x3}^*)$ , since  $v_{r4}^* = 0$ . Consequently, step 1 is not necessary and after step 2 (i.e.,  $v_{rj}^* = v_{pj}^*$ ), steps 3 and 4 determine the pole voltages for three full H-bridges.

# D. Choice of the parameters $\mu_{r4}^*$ and $\mu_{xk}^*$

In all three configurations, the reference pole voltages are compared with carrier signals in order to obtain the state of the power switches. The values of parameters  $\mu_{r4}^*$  and  $\mu_{xk}^*$  are chosen in order to reduce the harmonic distortion of the voltage generated by the converters A and B. The determination of parameters  $\mu_{xk}^*$  and the carriers disposition to solve the pole voltages calculation of equivalent H-bridge was done with a similar approach presented in [31].

Another alternative way for choosing parameters  $\mu_{r4}^*$  and  $\mu_{xk}^*$  is to consider their values in order to share the power processed between the dc links of converters A and B. This option permits to minimize the active power in one dc-link. In this way, such a dc-link could be considered as a very low energy storage source (e.g., a battery with low voltage rating) or even as a floating dc-link capacitor for fault tolerance capability.

#### IV. SYSTEM CONTROL

In DVR applications, open loop and closed loop are control methods well accepted and used in the literature [32]–[34]. In this paper, an open loop load voltage control, combined with feed forward compensation that deals with voltage drop caused by filter  $C_f$ , was considered. In this way, grid voltages  $(e_{gj})$  are measured and compared with rated load voltages  $(v_{tj}^*)$ . The comparison result gives the references to the injected voltages  $(v_{pj}^* = e_{gj} - v_{lj}^*)$ . A feed forward action can be used in order the compensated voltage drop  $(v_{cf})$  in the passive filters. Hence, the references become  $v_{pj}^* = e_{gj} - v_{lj}^* + v_{cf}$ . The voltage sag detection scheme used in this paper is similar to that one used in [34]. The reference voltages  $v_{pj}^*$  must be synchronized with  $e_{gj}$ . In this way, a phase-locked loop based on fictitious electrical power (i.e., power-based PLL) [35] was considered.

#### V. TOPOLOGICAL COMPARISON

The minimum dc-link voltage required (i.e.,  $v_{cab}^{*}$  for proposed or  $v_{c}^{*}$  for conventional) for each dc-link of the topologies investigated in this work was compared. This specification reflects on the peak inverse voltages (PIV) at each power switch. It can be seen also the number of semiconductor devices and capacitors needed for each topology. In this comparison two cases are considered with maximum balanced voltages in dq-frame: i) without zero sequence voltage  $(v_0)$  and ii) with zero sequence voltage injection  $(v_0)$ .

Table I presents a dc-link voltage comparison in which the converter produces a maximum balanced voltages with no zero sequence voltage. In this way, the three-phase voltages  $v_{pj}$  (i.e.,  $v_{p1}$ ,  $v_{p2}$  and  $v_{p3}$ ) are symmetrical and balanced as follows

$$v_{pj} = V_{pdq} sin(wt - 2(j-1)\pi/3)$$

(20)

where  $V_{pdq}$  is the maximum voltage amplitude in dq-frame available at the primary side of the injection transformers and  $w = 2\pi f_o$  in which  $f_o$  is the fundamental system frequency.

Then, considering the parameter  $v_{cab}^*$ , configurations 4L4L and 4L2C have presented a reduction of 56% in comparison with 2C topology. In comparison with the topology 4L, the configurations 4L4L and 4L2C can be reduced up to 50%. Lastly, the voltage  $v_{cab}^*$  for both of them (i.e., 4L4L and 4L2C) can be reduced up to 15% compared to conventional 3HB and proposed 2C2C. Nevertheless, they have a higher number of IGBTs as well as capacitors. The proposed 2C2C topology provides the same dc-link voltage rating if compared to 3HB one but it takes advantage of its different dc-link voltages operation capability. Hence, such a topology (2C2C) can generate the voltages  $v_{pj}$  with lower harmonic distortion in comparison with 3HB topology.

Taking into consideration conventional multilevel structures, similar comparison can be observed with a conventional four-leg neutral-point-clamped (4LNPC) configuration [28]. It can be seen that 4LNPC presents the same power switches count (i.e., 16 IGBTs) and dc-link capacitors (i.e., 2 capacitors) as for 4L4L. However, 4LNPC needs 8 additional clamping diodes that are not needed for any one of proposed configurations.

TABLE I TOPOLOGICAL COMPARISON.  $v_{cab}^*$  is for proposed configurations and  $v_c^*$  is for conventionals.

| Topology                                                                        | $v_{cab}^*$ or $v_c^*$                                                                        | <b>IGBTs</b>        | Capacitors                      |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------|---------------------------------|

| Conventional 2C                                                                 | $2.00V_{pdq}$                                                                                 | 6                   | 2                               |

| Conventional 3HB                                                                | $1.00V_{pdq}$                                                                                 | 12                  | 1                               |

| Conventional 4L                                                                 | $1.73V_{pdq}$                                                                                 | 8                   | 1                               |

| Conventional 4LNPC                                                              |                                                                                               | 16                  | 2                               |

| Proposed 4L4L                                                                   | $0.87V_{pdq}$                                                                                 | 16                  | 2                               |

| Proposed 2C2C                                                                   | $1.00V_{pdq}$                                                                                 | 12                  | 4                               |

| Proposed 4L2C                                                                   | $0.83V_{pdq}$                                                                                 | 14                  | 3                               |

| Conventional 3HB Conventional 4L Conventional 4LNPC Proposed 4L4L Proposed 2C2C | $ \begin{array}{c} 1.00 V_{pdq} \\ 1.73 V_{pdq} \\ 1.73 V_{pdq} \\ 0.87 V_{pdq} \end{array} $ | 8<br>16<br>16<br>12 | 1<br>1<br>2<br>2<br>2<br>4<br>3 |

For the case in which  $v_{pj}$  have zero sequence voltage  $(v_0)$ , the configurations 4L4L, 4L and 4L2C can generate a parcel of that voltage with the same dc-link value shown in Table I (obtained without zero sequence voltage). Hence, it can be written

$$v_{pj} = V_{pdq} sin(wt - 2(j-1)\pi/3) + V_{po} sin(wt)$$

(21)

where  $V_{po}$  is the maximum amplitude of the zero sequence voltage.

The maximum amplitude of  $V_{po}$  that can be achieved for each configuration is given by

• 4L4L and 4L:

$$V_{po} \le 0.732 V_{pdq} \tag{22}$$

4L2C:

$$V_{po} \le 0.2990 V_{pdq}$$

; if  $v_{ca} = v_{cb}$  (23)

$$V_{po} \le 0.1547 V_{pdg}$$

; if  $v_{ca} = v_{cb}/2$  (24)

$$V_{po} \le 0.4434 V_{pda}$$

; if  $v_{ca} = 2v_{cb}$  (25)

# VI. COMPARISON OF SWITCHING VECTORS AVAILABLE

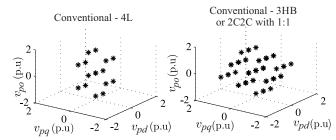

There are 16 ( $2^4$ ) and 64 ( $2^6$ ) switching states in the case of conventional 4L and 3HB based DVR, respectively. For 4L and 3HB configurations, those switching states generate 15 and 27 different switching vectors, respectively. Fig. 5 shows all vectors available for these conventional configurations in 3D (dqo space). Notice that 2C2C configuration with dc-link ratio 1:1 (that means  $v_{ca} = v_{cb}$ ) is equivalent to 3HB one.

Fig. 5. Output voltage space and the switching vectors available for conventional inverters. Conventional 4L (on the left). Conventional 3HB or 2C2C with dc-link ratio 1:1 (on the right).

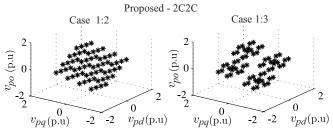

Fig. 6 shows the switching vectors available for the proposed 2C2C configuration considering two cases of dc-link

values: i) case 1:2 (that means  $v_{ca} = 2v_{cb}$ ) and ii) case 1:3 (meaning  $v_{ca} = 3v_{cb}$ ), both of them generating 64 different switching vectors. However, case 1:3 presents a more asymmetrical switching vectors distribution if compared to the case 1:2. Comparing with 3HB, proposed 2C2C with dc-link ratios of either 1:2 or 1:3 has also 64 switching states but it provides more different switching vectors (i.e., 64 instead of 27 obtained with 3HB).

Fig. 6. Output voltage space and the switching vectors available for proposed 2C2C. Operation with dc-link ratio 1:2 (on the left). Operation with dc-link ratio 1:3 (on the right).

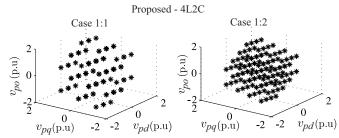

The proposed 4L2C configuration has 128 ( $2^7$ ) switching states. Then, as expected, the number of different vectors increases in comparison with the previous one, as observed in Fig. 7. In this result, case 1:1 ( $v_{ca} = v_{cb}$ ) presents 46 different switching vectors whereas case 1:2 ( $v_{ca} = 2v_{cb}$ ) has 101 different switching vectors. The case 1:3 for this configuration is not shown due to its more asymmetrical switching vectors distribution than that one obtained for case 1:2. Such a sort of deterioration is already shown in Fig. 6 for configuration 2C2C.

Fig. 7. Output voltage space and the switching vectors available for proposed 4L2C configuration. Operation with dc-link ratio 1:1 (on the left). Operation with dc-link ratio 1:2 (on the right).

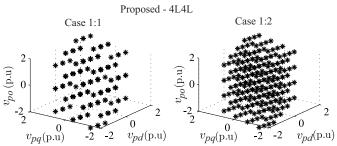

Fig. 8 shows a similar result for configuration 4L4L. Such a result shows that 65 different switching vectors are obtained in case 1:1 whereas 175 different switching vectors are obtained in case 1:2.

Comparing with the 2C2C and the conventional ones, it can be seen that both 4L2C and 4L4L provide high number of different switching vectors. However, some of them have high values of  $v_{po}$  component that maybe will not be used if the inverters operate with low  $v_{po}$  magnitude.

#### VII. HARMONIC DISTORTION

The weighted total harmonic distortion (WTHD) of the injected voltages  $(v_{pj})$  for conventional 3HB and proposed configurations have been computed by using

Fig. 8. Output voltage space and the switching vectors available for proposed 4L4L configuration with dc-link ratios 1:1 (on the left) and 1:2 ratio (on the right).

$$WTHD(p) = \frac{100}{a_1} \sqrt{\sum_{i=2}^{p} \left(\frac{a_i}{i}\right)^2}$$

(26)

where  $a_1$  is the amplitude of the fundamental voltage,  $a_i$  is the amplitude of  $i^{th}$  harmonic and p is the number of harmonics taken into consideration. Then, by imposing the same operation conditions that are a maximum injection of  $v_{pj}$  in a balanced three-phase case, WTHD of the injected voltages  $(v_{pj})$  for conventional 3HB and proposed configuration can be observed in Table II. In this result, both average switching frequency  $(f_s)$  and fundamental frequency  $(f_o)$  were fixed in 10 kHz and 50 Hz, respectively.

It should be noticed that 2C2C topology operating with dc-link ratio 1:1 ( $v_{ca} = v_{cb}$ ) is equal to conventional 3HB. Such cases permit to conclude that the best (minimum) WTHD value is achieved with proposed 4L4L. Nevertheless all proposed configurations present lower WTHD values in comparison with conventional 3HB that has best WTHD value among the conventional ones.

TABLE II WHTD FOR CONVENTIONAL AND PROPOSED CONFIGURATIONS ( $f_s=10$  kHz;  $f_o=50$  Hz).

| 1112, 70 00 112). |               |          |  |  |  |  |  |  |

|-------------------|---------------|----------|--|--|--|--|--|--|

| Topology          | Dc-link ratio | WTHD (%) |  |  |  |  |  |  |

| Conventional 3HB  | -             | 0.22     |  |  |  |  |  |  |

| Proposed 2C2C     | 1:2           | 0.14     |  |  |  |  |  |  |

| Floposed 2C2C     | 1:3           | 0.15     |  |  |  |  |  |  |

|                   | 1:1           | 0.19     |  |  |  |  |  |  |

| Proposed 4L2C     | 1:2           | 0.12     |  |  |  |  |  |  |

|                   | 1:3           | 0.34     |  |  |  |  |  |  |

|                   | 1:1           | 0.12     |  |  |  |  |  |  |

| Proposed 4L4L     | 1:2           | 0.11     |  |  |  |  |  |  |

|                   | 1:3           | 0.11     |  |  |  |  |  |  |

#### VIII. CONVERTER POWER LOSSES

The loss estimation was obtained through regression model, which has been achieved by experimental tests as presented in [36] and [37]. The thermal module, an existing tool in PSIM v9.0 was used with calibration parameters that gives an equivalent estimation. The power switch used in the experimental tests was: IGBT dual module CM50DY-24H (POWEREX) driven by SKHI-10 (SEMIKRON). The switch losses model includes: a) IGBT and diode conduction losses; b) IGBT turnon losses; c) IGBT turn-off losses; d) Diode turn-off energy.

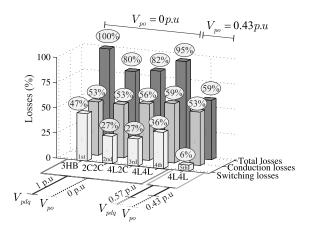

Fig. 9 shows a result with five cases in which the proposed DVR configuration losses have been compared with

the conventional 3HB under the same operation conditions (i.e., four cases with maximum balanced three-phase voltages without zero sequence component and a fifth case with zero sequence component) and with the same harmonic distortion content (WTHD = 0.22%) for  $v_{pj}$ . For instance, the average switching frequency  $(f_s)$  has been fixed in 10 kHz, 6.25 kHz, 5.3 kHz and 4.8 kHz for 3HB, 2C2C, 4L2C and 4L4L, respectively. Such values guarantee that DVRs will generate the voltages  $v_{pj}$  with the same harmonic distortion. Different dc-link voltage values were considered (i.e., 1:2). The results have been normalized with conventional 3HB (total losses close to 58 W). Notice that the proposed configurations present lower switching losses and increased conduction losses on the proposed configuration as a consequence of their high number of IGBTs. Nevertheless, the total losses are lower in comparison with conventional 3HB.

Fig. 9. Semiconductor losses comparison between conventional 3HB and proposed configurations operating with dc-link ratio 1:2 under the same harmonic distortion content at  $v_{pj}$ . First four results (from the left to right) with  $V_{po}=0$  and fifth result with 57% of  $V_{pdq}$  and 43% of  $V_{po}$ .

The fourth leg connected to the neutral will improve the performance of the system under zero-sequence voltage compensation as well as offers the possibility to control zerosequence voltage. In this case, the fifth result of losses in Fig. 9 shows a case for configuration 4L4L in which 57% of  $V_{pdq}$  is compensated leading 43% of compensation for  $V_{po}$ . In this way, the converter can operate with dc-link voltage  $(v_{ca} + v_{cb})$  equal to  $\sqrt{3}V_{pdq}$  (the same value used for  $V_{po} = 0$ ). Additionally, the voltage waveforms of  $v_{pj}$ are improved in terms of WTHD, which permits to reduce switching frequency up to 2.55 kHZ to maintain the same WTHD of  $v_{pj}$  obtained for the other cases (i.e., WTHD = 0.22%). Hence, the possibility to hand out the zero-sequence to fourth leg justifies: i) dc-link voltage reduction and ii) the waveform quality of  $v_{pj}$  that leads switching frequency reduction to operate under the same WTHD of conventional 3HB. Asymmetric dc-link voltage operation was employed in this result (i.e., dc-link voltage ratio 1:2).

#### IX. DC-LINK HIGH FREQUENCY POWER LOSSES

In this section, a comparative study of dc-link power losses estimation has been made. In this case, the operation of conventional and proposed configurations was fixed with the same WTHD conditions for the injected voltages  $(v_{pj})$ .

The dc-link high frequency power losses is calculated by

$$P_{loss}^{HO} = N(0.45)ESR_{(100Hz)} \left(I_{c,rms}^{HO}\right)^2 \tag{27}$$

where N is the number of capacitors used in each topology,  $I_{c,rms}^{HO}$  is the component of the high-order of the root mean square (RMS) current on the dc-link (with h>50) and  $ESR_{(100Hz)}$  is the equivalent series resistance for a frequency of 100 Hz. The ESR can be considered constant for frequency higher than 3 kHz. It is equal to 0.45 times of ESR value for 100 Hz [38]. This means that  $P_{loss}^{HO}$  depends only of the  $I_{loss}^{HO}$

Fig. 10 shows harmonic spectrum of dc-link currents for comparison purposes with different dc-link voltage values (i.e., considering dc-link ratio 1:2). It can be observed that the equivalent harmonic current content for proposed OEW configurations does not exceed the magnitude of conventional 3HB one.

Fig. 10. Harmonic spectrum of the capacitor currents for conventional 3HB and proposed configurations.

Table III presents the dc-link high frequency power losses normalized by power losses of conventional 3HB configuration (i.e,  $P_{loss}^{HO}/P_{loss(3HB)}^{HO}$ ). Notice that the proposed 4L4L presents a reduction of 64% in dc-link high frequency power losses compared to conventional 3HB, whereas 2C2C and 4L2C presented a reduction of 23% and 39%, respectively.

$\begin{tabular}{l} TABLE~III\\ LOSSES~COMPARISON~OF~THE~DC-LINK. \end{tabular}$

| Normalized dc-link losses          |      |      |      |      |  |  |  |

|------------------------------------|------|------|------|------|--|--|--|

| Topology                           | ЗНВ  | 2C2C | 4L2C | 4L4L |  |  |  |

| $P_{loss}^{HO}/P_{loss(3HB)}^{HO}$ | 1.00 | 0.77 | 0.61 | 0.36 |  |  |  |

#### X. SIMULATION RESULTS

Conventional 3HB and proposed DVR configurations have been evaluated through simulation by using PSIM v9.0 and MATLAB<sup>®</sup>. The dc-link voltages were considered as auxiliary energy DC sources (i.e., isolated batteries). The simulation step (h) was fixed in 0.5  $\mu$ s and the switching frequency  $(f_s)$  was considered as 10 kHz. The load type was considered as resistance bank of 100  $\Omega$ .

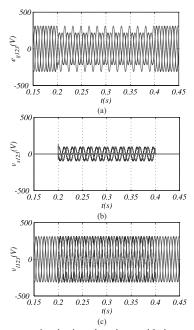

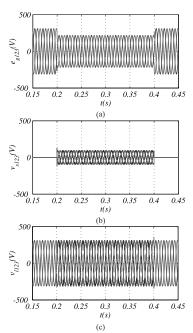

Fig. 11 shows the injected voltages (not filtered) by DVR considering equal  $(v_{ca} = v_{cb})$  and different  $(v_{ca} \neq v_{cb})$  dc-link voltage values for proposed configurations. The cases investigated in Fig. 11 show that the injected voltages by the proposed DVRs provide more levels and as a consequence they present lower WTHD in comparison with the conventional 3HB one under the same conditions of operation.

Fig. 11. Injected voltages by the DVR considering conventional 3HB topology and proposed configurations with equal dc-link voltages ( $v_{ca} = v_{cb} \rightarrow$  dc-link ratio 1:1) and different dc-link voltages ( $v_{ca} \neq v_{cb} \rightarrow$  dc-link ratios 1:2 and 1:3).

The system performance with proposed DVR 4L4L operating with equal dc-link voltages ( $v_{ca}=v_{cb}$ ) has been investigated under: i) single-phase voltage sag (see Fig. 12), ii) two-phase voltage sag (see Fig. 13) and iii) three-phase voltage sag (see Fig. 14). The magnitude of the voltage sag was the same for three cases (i.e., 30%) with time duration close to 200 ms. It can be seen that the proposed 4L4L DVR

compensated the voltage sags satisfactorily. The results for configurations 2C2C, 4L2C are similar.

Fig. 12. System operation in time domain considering configuration 4L4L. The DVR compensates a 30% single-phase voltage sag. (a) Grid voltages. (b) Injected voltages by the DVR. (c) Load voltages.

Fig. 13. System operation in time domain considering configuration 4L4L. The DVR compensates a 30% two-phase voltage sag. (a) Grid voltages. (b) Injected voltages by the DVR. (c) Load voltages.

#### XI. EXPERIMENTAL SYSTEM SPECIFICATIONS

The Proposed DVRs, shown in Fig. 3, have been validated in laboratory via some experimental tests. Such tests were made with a downscaled prototype system. The grid line-neutral voltage was considered as 70 V (RMS) and the

Fig. 14. System operation in time domain considering configuration 4L4L. The DVR compensates a 30% three-phase voltage sag. (a) Grid voltages. (b) Injected voltages by the DVR. (c) Load voltages.

voltage sag generator was implemented with 50  $\Omega$  / 200 W resistors connected in series with the downscaled grid. The load type considered in the tests was a resistors bank (incandescent lamps). The dc-link voltages of the converters A and B were obtained from two rectifiers (isolated from each other) connected to ac-lines by means of an auxiliary autotransformer.

The dc-link capacitors were selected as  $C=2200~\mu\mathrm{F}$ , the switching frequency  $(f_s)$  employed was 10 kHz. The three used injection transformers have a power rated equal to 1 kVA each, with turn ratios from the primary to the secondary winding equal to 1:1. The core of the transformers is made of ferromagnetic grain-oriented material in a toroidal shape. Such a characteristic minimizes their leakage inductance. Three capacitors  $C_f$  were connected at the secondary winding of each injection transformer in order to filter high order harmonics provided from the PWM converters. The filtering capacitors were selected as  $C_f=30~\mu\mathrm{F}$ .

The converters used for the prototype are composed of IG-BTs power switches from semikron (SKM50GB123D) driven by SKHI23, which receives gating signals throughout optical fiber cables linked to a digital signal processor (DSP) TMS320F28335 with a microcomputer equipped with appropriated plug-in boards and sensors.

#### XII. EXPERIMENTAL RESULTS

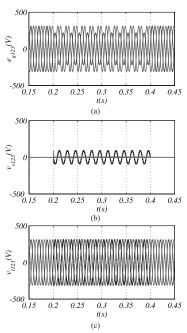

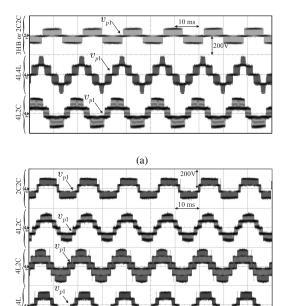

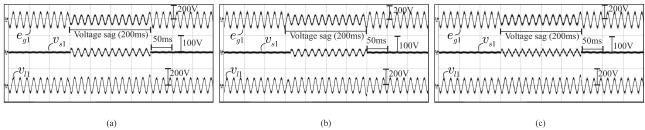

Experimental results presented in Fig. 15 show the PWM validation for the proposed DVRs. The phase-voltage at the primary side of the transformer  $(v_{p1})$  is presented for one phase for each configuration. Fig. 15(a) shows the operation with  $v_{Ca} = v_{Cb}$  (i.e., dc-link ratio 1:1) whereas the cases of different dc-link voltages (i.e., dc-link ratio 1:2) are shown in

Fig. 15. Experimental results. Voltage  $v_{p1}$  for each proposed configuration and conventional 3HB (or 2C2C). (a) 3HB or 2C2C (top), 4L4L (middle) and 4L2C (bottom) operating with dc-link ratio 1:1 ( $v_{ca}=v_{cb}=100\,$  V). (b) 2C2C (top), 4L2C (middle 1:  $v_{ca}=67\,$  V and  $v_{cb}=133\,$  V), 4L2C (middle 2:  $v_{ca}=133\,$  V and  $v_{cb}=67\,$  V) and 4L4L (bottom) operating with dc-link ratio 1:2 ( $v_{ca}=133\,$  V and  $v_{cb}=67\,$  V).

(b)

Fig. 16. Experimental results. Injected voltages by DVR with 4L4L configuration compensating 35% of zero sequence component. The inverters operate with  $v_{ca}=133$  V and  $v_{cb}=67$  V.

Fig. 15(b). It can be observed that these outcomes are similar to simulation results presented previously in Fig. 11.

Fig. 16 shows results in which the configuration 4L4L processes 50% of dq voltage component and 35% of zero sequence component. In this way, the references are

$$v_{pj} = 0.5V_{pdq}sin(wt - 2(j-1)\pi/3) + V_{po}sin(wt)$$

(28)

with

$$V_{pdq} = 2v_{cab}^*/\sqrt{3}$$

and  $V_{po} = 0.35V_{pdq}$ .

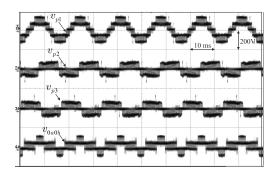

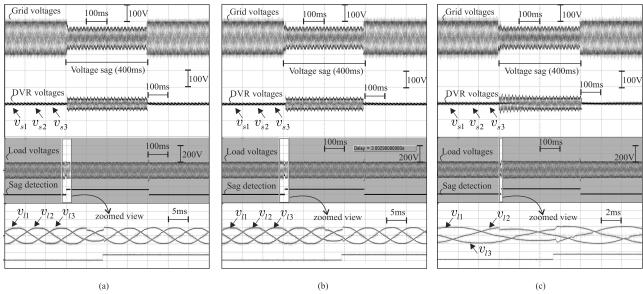

The dynamic operation of the proposed DVRs has been tested experimentally. Fig. 17 shows results in which the DVRs compensate an unbalanced 35% three-phase voltage sag with time duration close to 400 ms. It can be seen that the load voltages are well compensated. The time interval between the voltage sag occurrence and the DVR action was close to 4 ms for the three configurations. The voltage transients (spikes)

Fig. 17. Experimental results. System voltages considering three proposed DVR configurations operating with asymmetric dc-link voltages under an unbalanced 35% three-phase voltage sag with 400 ms duration. (a) Proposed 4L4L. (b) Proposed 4L2C. (c) Proposed 2C2C.

Fig. 18. Experimental results. System voltages at phase 1 considering three proposed DVR configurations operating with asymmetric dc-link voltages under 40% single-phase voltage sag with 200 ms duration. (a) Proposed 4L4L. (b) Proposed 4L2C. (c) Proposed 2C2C.

observed on the load voltages both at the start or return transition of voltage sag are due to the filtering capacitors  $(C_f)$ . This phenomena was observed also in some studies in the literature and can be attenuated with a more accurate control method or by using a robust passive filter (e.g., LCL filter type) as discussed in [32], [34].

Fig. 18 shows the DVR compensation under a 40% single-phase voltage sag generated at the grid voltage  $(e_{g1})$  during 200 ms, with proposed configurations operating with different dc-link voltages. In this way, once the voltage sag is detected the converters start to operate by applying voltage directly at the primary side of injection transformer. This voltage is filtered by filtering capacitors  $C_f$  giving the necessary voltage  $v_{s1}$  to be compensated by the DVR. Outcomes are shown only for the disturbed phase (i.e., phase 1). It can be seen that the load voltage  $(v_{l1})$  keeps its magnitude fixed at 1 p.u that means a satisfactory compensation. Fig. 18(a) shows results for 4L4L configuration operating with  $v_{ca} = 2v_{cb}$ . The same scenario considering topology 4L2C is shown in Fig. 18(b) in which the dc-link voltage ratio is  $v_{ca} = 0.5v_{cb}$ . The result is shown similarly for configuration 2C2C in Fig. 18(c) with  $v_{ca} = 2v_{cb}$ .

# XIII. CONCLUSION

In this paper, three four-wire dynamic voltage restorers (DVRs) have been proposed. The studied configurations are

based on the concept of open-end winding. Compared to conventional 3HB, the proposed ones have presented advantages in terms of lower WTHD, semiconductor losses, dc-link high frequency losses and low dc-link voltage rating. On the other hand, 4L4L and 4L2C topologies have an increased switch count. It is noted that the dc-link voltage reduction is more evident for configurations 4L4L and 4L2C with the increasing of the zero sequence voltage magnitude  $(V_{po})$ . This is because the zero sequence parcel can only be fully controlled by the fourth legs of each converter (i.e., 2 legs for 4L4L and 1 leg for 4L2C). For configuration 3HB and 2C2C this flexibility is lost because the zero-sequence voltage will be controlled over the six legs connected to the wires 1, 2 and 3 of the DVR. However, the maximum value achieved by  $V_{po}$  will be different accordingly to each configuration, as discussed in Section V.

The outcomes have shown that proposed DVRs are feasible and suitable for three-phase four-wire (3P4W) power distribution systems in which low harmonic distortion is a priority since it leads to reduce the switching frequency to match the same WTHD value that is obtained with conventional configuration. However, notice that conventional one will operate with higher frequency rating. The proposed configurations have advantages in high-voltage systems that would be unlikely to be achieved with some conventional configurations (e.g., 2C and 4L configurations).

#### REFERENCES

- W. Brumsickle, G. Luckjiff, R. Schneider, D. Divan, and M. Mc-Granaghan, "Dynamic sag correctors: cost effective industrial power line conditioning," in *Industry Applications Conference*, 1999. Thirty-Fourth IAS Annual Meeting. Conference Record of the 1999 IEEE, vol. 2, pp. 1339–1344 vol.2, 1999.

- [2] M. McGranaghan, D. Mueller, and M. Samotyj, "Voltage sags in industrial systems," *Industry Applications, IEEE Transactions on*, vol. 29, no. 2, pp. 397–403, 1993.

- [3] C.-m. Ho and H.-H. Chung, "Implementation and performance evaluation of a fast dynamic control scheme for capacitor-supported interline DVR," *Power Electronics, IEEE Transactions on*, vol. 25, no. 8, pp. 1975–1988, 2010.

- [4] I. Pires, S. Silva, and B. Filho, "Increasing ride-through capability of control panels using square-wave series voltage compensator," *Industry Applications, IEEE Transactions on*, vol. 51, pp. 1309–1316, March 2015.

- [5] T. Jimichi, H. Fujita, and H. Akagi, "Design and experimentation of a dynamic voltage restorer capable of significantly reducing an energystorage element," *Industry Applications, IEEE Transactions on*, vol. 44, pp. 817–825, May 2008.

- [6] A. Ghosh and G. Ledwich, "Compensation of distribution system voltage using DVR," *Power Delivery, IEEE Transactions on*, vol. 17, no. 4, pp. 1030–1036, 2002.

- [7] J. Nielsen, M. Newman, H. Nielsen, and F. Blaabjerg, "Control and testing of a dynamic voltage restorer (DVR) at medium voltage level," *Power Electronics, IEEE Transactions on*, vol. 19, no. 3, pp. 806–813, 2004.

- [8] P. Jayaprakash, B. Singh, D. Kothari, A. Chandra, and K. Al-Haddad, "Control of reduced-rating dynamic voltage restorer with a battery energy storage system," *Industry Applications, IEEE Transactions on*, vol. 50, pp. 1295–1303, March 2014.

- [9] Y. W. Li, D. Vilathgamuwa, F. Blaabjerg, and P. C. Loh, "A robust control scheme for medium-voltage-level DVR implementation," *Industrial Electronics*, *IEEE Transactions on*, vol. 54, no. 4, pp. 2249–2261, 2007.

- [10] I.-Y. Chung, S.-Y. Park, S.-I. Moon, and S.-I. Hur, "The control and analysis of zero sequence components in DVR system," in *Power Engineering Society Winter Meeting*, 2001. IEEE, vol. 3, pp. 1021–1026 vol.3, 2001.

- [11] N. Woodley, L. Morgan, and A. Sundaram, "Experience with an inverter-based dynamic voltage restorer," *Power Delivery, IEEE Transactions on*, vol. 14, no. 3, pp. 1181–1186, 1999.

- [12] C. Zhan, A. Arulampalam, and N. Jenkins, "Four-wire dynamic voltage restorer based on a three-dimensional voltage space vector PWM algorithm," *Power Electronics, IEEE Transactions on*, vol. 18, no. 4, pp. 1093–1102, 2003.

- [13] A. Tashackori, S. Hosseini, M. Sabahi, and T. Nouri, "A three-phase four-leg DVR using three dimensional space vector modulation," in *Electrical Engineering (ICEE)*, 2013 21st Iranian Conference on, pp. 1– 5, 2013

- [14] S. Naidu and D. Fernandes, "Generation of unbalanced 3-phase voltages for dynamic voltage restoration using the 4-leg voltage source converter," in *Power Electronics Specialists Conference*, 2007. PESC 2007. IEEE, pp. 1195–1200, 2007.

- [15] J. Nielsen and F. Blaabjerg, "A detailed comparison of system topologies for dynamic voltage restorers," *Industry Applications, IEEE Transactions* on, vol. 41, pp. 1272–1280, Sept 2005.

- [16] A. Rauf and V. Khadkikar, "Integrated photovoltaic and dynamic voltage restorer system configuration," Sustainable Energy, IEEE Transactions on, vol. 6, pp. 400–410, April 2015.

- [17] M. Newman, D. Holmes, J. Nielsen, and F. Blaabjerg, "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level," *Industry Applications, IEEE Transactions on*, vol. 41, pp. 1744–1753, Nov 2005.

- [18] G. Chen, L. Zhang, R. Wang, L. Zhang, and X. Cai, "A novel spll and voltage sag detection based on les filters and improved instantaneous symmetrical components method," *Power Electronics, IEEE Transac*tions on, vol. 30, pp. 1177–1188, March 2015.

- [19] D. Fernandes, F. Costa, and M. Vitorino, "A method for averting saturation from series transformers of dynamic voltage restorers," *Power Delivery, IEEE Transactions on*, vol. 29, pp. 2239–2247, Oct 2014.

- [20] S. Silva, S. da Silveira, A. Reis, and B. Filho, "Analysis of a dynamic voltage compensator with reduced switch-count and absence of energy storage system," *Industry Applications, IEEE Transactions on*, vol. 41, pp. 1255–1262, Sept 2005.

- [21] A. Prasai and D. Divan, "Zero-energy sag correctors optimizing dynamic voltage restorers for industrial applications," *Industry Appli*cations, IEEE Transactions on, vol. 44, pp. 1777–1784, Nov 2008.

- [22] T. Jimichi, H. Fujita, and H. Akagi, "An approach to eliminating DC magnetic flux from the series transformer of a dynamic voltage restorer," *Industry Applications, IEEE Transactions on*, vol. 44, pp. 809–816, May 2008

- [23] P. Kanjiya, B. Singh, A. Chandra, and K. Al-Haddad, "SRF theory revisited to control self-supported dynamic voltage restorer (DVR) for unbalanced and nonlinear loads," *Industry Applications, IEEE Transac*tions on, vol. 49, pp. 2330–2340, Sept 2013.

- [24] T. Jimichi, H. Fujita, and H. Akagi, "A dynamic voltage restorer equipped with a high-frequency isolated DC-DC converter," *Industry Applications, IEEE Transactions on*, vol. 47, pp. 169–175, Jan 2011.

- [25] Y.-W. Li, P.-C. Loh, F. Blaabjerg, and D. Vilathgamuwa, "Investigation and improvement of transient response of DVR at medium voltage level," *Industry Applications, IEEE Transactions on*, vol. 43, pp. 1309–1319, Sept 2007.

- [26] B. Wang and G. Venkataramanan, "Dynamic voltage restorer utilizing a matrix converter and flywheel energy storage," *Industry Applications*, *IEEE Transactions on*, vol. 45, pp. 222–231, Jan 2009.

- [27] J. Shi, Y. Tang, K. Yang, L. Chen, L. Ren, J. Li, and S. Cheng, "SMES based dynamic voltage restorer for voltage fluctuations compensation," Applied Superconductivity, IEEE Transactions on, vol. 20, pp. 1360–1364, June 2010.

- [28] J.-H. Kim, S.-K. Sul, and P. Enjeti, "A carrier-based PWM method with optimal switching sequence for a multilevel four-leg voltagesource inverter," *Industry Applications, IEEE Transactions on*, vol. 44, pp. 1239–1248, July 2008.

- [29] O. Lopez, J. Alvarez, J. Doval-Gandoy, F. Freijedo, A. Lago, and C. Penalver, "Four-dimensional space vector pwm algorithm for multilevel four-leg converters," in *Industrial Electronics*, 2008. IECON 2008. 34th Annual Conference of IEEE, pp. 3252–3259, Nov 2008.

- [30] V. Somasekhar, K. Gopakumar, M. Baiju, K. Mohapatra, and L. Umanand, "A multilevel inverter system for an induction motor with open-end windings," *Industrial Electronics, IEEE Transactions on*, vol. 52, no. 3, pp. 824–836, 2005.

- [31] G. de Almeida Carlos, E. dos Santos, C. Jacobina, and J. Mello, "Dynamic voltage restorer based on three-phase inverters cascaded through an open-end winding transformer," *Power Electronics, IEEE Transactions on*, vol. 31, pp. 188–199, Jan 2016.

- [32] P.-T. Cheng, C.-C. Huang, C.-C. Pan, and S. Bhattacharya, "Design and implementation of a series voltage sag compensator under practical utility conditions," *Industry Applications, IEEE Transactions on*, vol. 39, pp. 844–853, May 2003.

- [33] M. Vilathgamuwa, A. Perera, S. Choi, and K. Tseng, "Control of energy optimized dynamic voltage restorer," in *Industrial Electronics Society*, 1999. IECON '99 Proceedings. The 25th Annual Conference of the IEEE, vol. 2, pp. 873–878 vol.2, 1999.

- [34] J. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," in Applied Power Electronics Conference and Exposition, 2001. APEC 2001. Sixteenth Annual IEEE, vol. 2, pp. 1267–1273 vol.2, 2001.

- [35] R. Santos Filho, P. Seixas, P. Cortizo, L. Torres, and A. Souza, "Comparison of three single-phase pll algorithms for UPS applications," *Industrial Electronics, IEEE Transactions on*, vol. 55, pp. 2923–2932, Aug 2008.

- [36] M. Cavalcanti, E. da Silva, D. Boroyevich, W. Dong, and C. Jacobina, "A feasible loss model for IGBT in soft-switching inverters," in *Power Electronics Specialist Conference*, 2003. PESC '03. 2003 IEEE 34th Annual, vol. 4, pp. 1845–1850 vol.4, June 2003.

- [37] J. A. A. Dias, E. dos Santos, C. Jacobina, and E. R. C. Da Silva, "Application of single-phase to three-phase converter motor drive systems with IGBT dual module losses reduction," in *Power Electronics Conference*, 2009. COBEP '09. Brazilian, pp. 1155–1162, Sept 2009.

- [38] J. Kolar and S. Round, "Analytical calculation of the RMS current stress on the dc-link capacitor of voltage-PWM converter systems," *Electric Power Applications, IEE Proceedings* -, vol. 153, pp. 535–543, July 2006.